📂 목차

📚 본문

운영체제의 상당 부분이 I/O 관리를 위해 있다. I/O 는 시스템의 신뢰성과 성능에 매우 민감하고, 장치들의 형태와 특성이 다양하기 때문에 이 기능에 초점을 맞춘다.

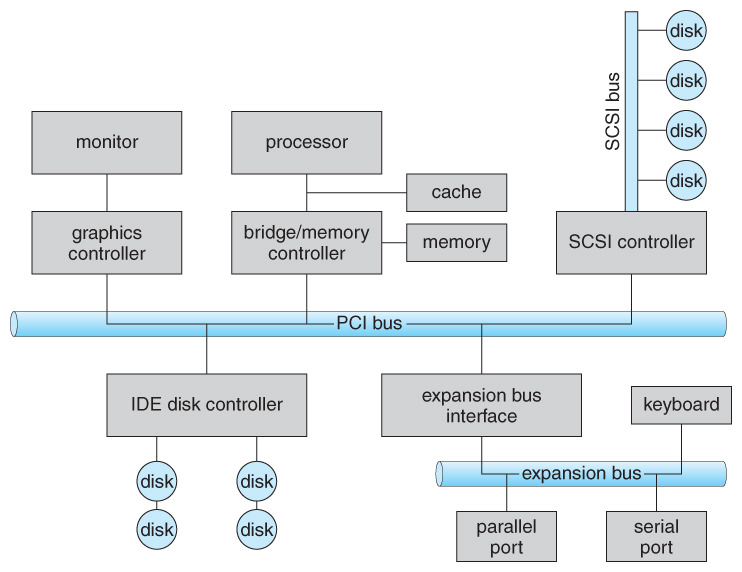

공통버스를 통한 데이터 전송의 한계점

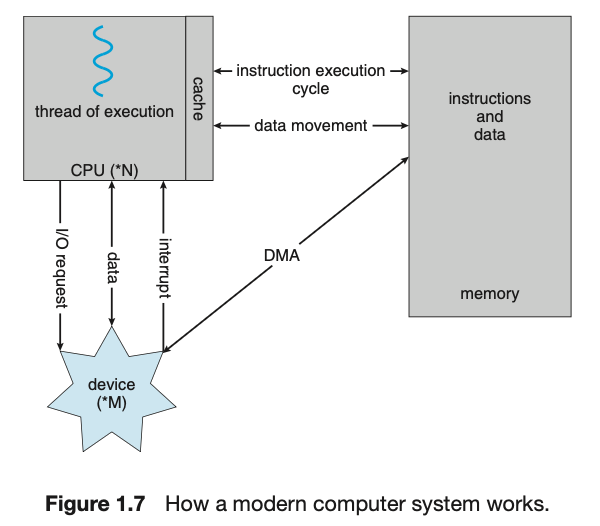

이전의 인터럽트 I/O 방식을 통해 명령을 수행하는 과정을 보자.

- CPU 가 Control Bus 와 Address Bus 를 통해 Device Controller 에게 명령 전달

- 수신 받은 Device Controller 는 I/O Device 와 직접 통신하여 해당 작업을 수행

- 여기서 Device Controller 는 자체 Local Buffer로 데이터를 준비하고 있는 상태임

- I/O 작업이 완료되고, Device Controller 는 인터럽트 신호를 Control Bus를 통해 CPU에게 보냄

- CPU 가 인터럽트를 감지하여 Context Switching 을 한 후, Interrupt Handler 를 호출

- 이 과정에서 인터럽트 벡터 테이블의 핸들러 주소를 조회

- CPU가 Interrupt Handler Code 에서 Device Controller 로 부터 처리된 데이터를 요청

- CPU가 Interrupt 처리 완료 후 실행중인 Context로 복귀

모든 장치가 단일 System Bus를 공유하므로, 다중 장치가 동시에 데이터를 전송하거나 수신하려고 할 경우 버스 충돌 및 지연(latency) 이 발생한다.

DMA를 통한 한계점 해결

DMA(직접 메모리 접근, Direct Memory Access) 의 데이터 전송 방식은 장치 버퍼, 포인터, 카운터 등을 설정하여서 장치 컨트롤러가 CPU 개입이 없이 장치와 주기억 장치 사이에서 전체 데이터 블록(Block)을 직접 전송하는 기술이다.

이때 데이터 블록 단위로 한 번의 인터럽트만 발생하여서, 작업 완료를 Device Driver 에 알리게 된다. 하지만 여기에도 단점이 있는데 시스템 버스는 단일 버스를 공유하기 때문에 사용중인 버스를 다른 장치 디바이스에서 전송은 불가하다(동시 전송 불가).

그래서 버스를 사용하려면 권한을 순서대로 조율해야 한다(Bus Arbitration). 이는 따라서 대량의 데이터 이동(NVS I/O 등) 에는 과도한 오버헤드를 유발한다.

Switch 구조를 통한 DMA 효율 상승

일부 고성능 시스템에서는 시스템 버스 구조가 아닌 스위치 구조를 사용하여 여러 컴포넌트 간에 동시에 서로 통신 할 수 있게 하여 공유된 버스에서 사이클을 경쟁하지 않아도 되는 DMA의 효율이 더욱 높아지게 된다.

바이트마다 인터럽트를 발생시키는 방식에 비해 훨씬 효율적이며, Device Controller 가 전송 작업을 수행하는 동안, CPU는 다른 작업을 수행할 수 있기 때문에 전체 시스템 효율이 높아진다.

| 방식 | CPU 개입 | 인터럽트 발생 | 효율성 |

|---|---|---|---|

| Programmed I/O(옛날 방식) | 높음 | 없음 | 낮음 |

| Interrupt I/O | 중간 | 매 I/O 이벤트 | 중간 |

| DMA | 낮음 | 전송 완료 시 | 높음 |